# **ED-WP-CB Data Sheet**

### Abstract

ED-WP-CB is a high-performance digital gate driver core developed by Firstack for NPC I-type /ANPC 3-level system. The gate driver adopts CPLD as the digitally controlled core, with complete protection functions and built-in fault management system, which uploads the converter's operating state to the master computer in real time, providing support for "big data management" for the failed converter site. Perfectly solving the two major problems of "turn-off timing sequence" and "large commutation circuit turn-off peak" in NPC I-type topology, the reliability of NPC topology can be comparable to 2-level, allowing customers to use NPC I-type /ANPC 3-level as same as 2-level.

Fig. 1 ED-WP-CB

#### Highlights:

- ✓ Multi-parallel of NPC/ANPC topology

- ✓ Rated voltage range:690-1250VAC

- ✓ Power range:1MW-10MW

#### **Applications:**

- ✓ PV inverter

- ✓ ESS

- ✓ Wind power converter

# Contents

| Abstract1                               |

|-----------------------------------------|

| Functional block diagram                |

| Use steps and matters needing attention |

| Mechanical dimensions                   |

| LED status indication                   |

| Pin definition                          |

| Driving parameters                      |

| Function description                    |

| Short-circuit protection                |

| • Undervoltage protection               |

| • Muti-level turn-off (reserved)        |

| • Short pulse suppression               |

| • NTC sampling                          |

| Fault code return (reserved)            |

| • Intelligent fault management system   |

| Ordering information                    |

| Technical support                       |

| Legal disclaimer                        |

| Contact information                     |

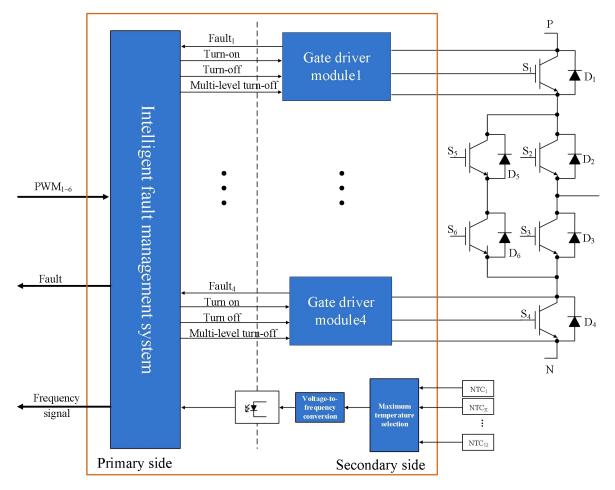

# Functional block diagram

Fig. 2 Functional block diagram

### Use steps and matters needing attention

Simple use steps of the gate driver are as follows:

1. Choose suitable gate driver

When use the gate driver, pay attention to the model of the IGBT module that the gate driver is adapted to. It is invalid for non-designated IGBT modules. Improper use may cause the gate driver and the module failure.

2. Install the gate driver on the IGBT module

Any treatment of IGBT modules or gate drivers should follow the general specifications for the protection of electrostatic sensitive devices required by the international standard IEC 60747-1, Chapter IX or European standard EN 61340-5-1.

If these specifications were ignored, both the IGBT

and the gate driver might be damaged.

3. Connect the gate driver to the control unit

Connect the gate driver connector to the control unit and provide a suitable power supply voltage for the gate driver.

4. Check the function of the gate driver

Check the gate voltage: for the turn-off state, the rated gate voltage is given in the corresponding data sheet; for the turn-on state, the voltage is 15V. Please also check the input current of the gate driver with and without a control signal. These tests should be performed prior to installation, as the gate terminals may not be accessible after installation.

5. Set up and test the power unit

Before starting the system, it is recommended to check each IGBT module with single pulse and double pulse test method separately. In particular, Firstack recommends that users ensure that the IGBT module does not exceed the operating range specified by SOA even under the worst conditions, as this is strongly dependent on the specific converter architecture.

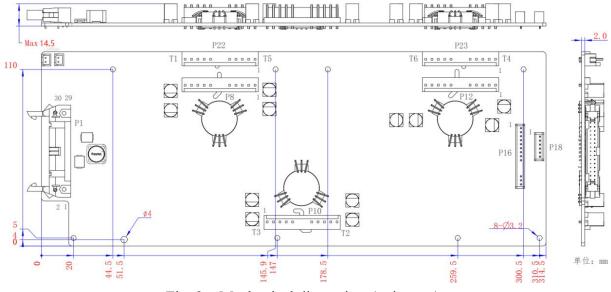

## **Mechanical dimensions**

Fig. 3 Mechanical dimensions(unit: mm)

Note: 1. The tolerance of the board thickness is  $\pm 10\%$ ;

2. Other dimensional tolerances refer to GB/T1804-m;

3.All mounting holes in the diagram must be used as a fixing, otherwise the connector is likely to cause damage to the gate driver due to excessive insertion and extraction stress. At the same time, the mounting holes must be fixed with plastic studs or other insulating material studs, otherwise there is a risk of safety issue.

| Number | Label                     | Manufacturer | Part Number      | Recommended<br>Matching<br>Terminals |

|--------|---------------------------|--------------|------------------|--------------------------------------|

| 1      | P1                        | Nextron      | Z-230011830209   | FC-30P                               |

| 2      | P8, P10, P12,<br>P22, P23 | WCON         | WF3963-WSH12B02  | WF3963-H12B01                        |

| 3      | P16                       | WCON         | WF2501A-WSH15B02 | WF2501A-H15B01                       |

| 4      | P18                       | WCON         | WF2501A-WSH06B05 | WF2501A-H06B01                       |

| 5      | P20, P21                  | JST          | B2B-XH-A         | XHP-2                                |

#### **Connector Manufacturer and Part Number**

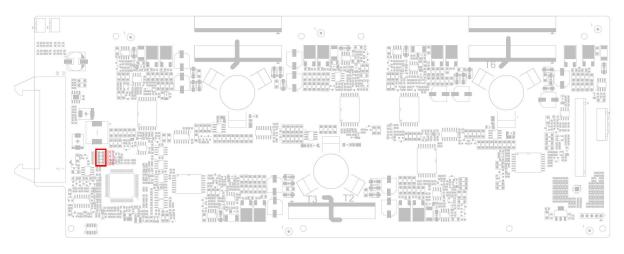

# LED status indication

Fig. 4 Status indicator

For the convenience of customers, several LED status indicators are added on the Firstack gate driver board to facilitate customers to know the operating status of the gate driver board and converter. The specific explanation is as follows:

| Number | Label | Interface | Note                                                                                            | Colour |

|--------|-------|-----------|-------------------------------------------------------------------------------------------------|--------|

| 1      | D19   | UV        | Once undervoltage trigger is always on, unless restarted.                                       | Red    |

| 2      | D15   | TEST      | Light on when the primary power supply is normal and there is no fault, otherwise it turns off. | Green  |

| 3      | D13   | SC        | Once short-circuit trigger is always on, unless restarted.                                      | Red    |

| 4      | D10   | 0Т        | Once over-temperature trigger is always on unless restarted (reserved).                         | Red    |

#### **Status Indicator**

# Pin definition

| Р   | P1 pin definition: |                     |     |                 |                     |  |  |  |

|-----|--------------------|---------------------|-----|-----------------|---------------------|--|--|--|

| Pin | Name               | Description         | Pin | Name            | Description         |  |  |  |

| 1   | NC                 | Free                | 2   | V <sub>DC</sub> | +15V power supply   |  |  |  |

| 3   | V <sub>DC</sub>    | +15V power supply   | 4   | V <sub>DC</sub> | +15V power supply   |  |  |  |

| 5   | GND                | Primary side ground | 6   | SO              | Fault summary       |  |  |  |

| 7   | GND                | Primary side ground | 8   | GND             | Primary side ground |  |  |  |

| 9   | GND                | Primary side ground | 10  | IN1             | T1 PWM signal       |  |  |  |

| 11  | GND                | Primary side ground | 12  | PT1-1           | External PT1 pin1   |  |  |  |

| 13  | PT1-2              | External PT1 pin2   | 14  | NC              | Free                |  |  |  |

| 15  | GND                | Primary side ground | 16  | IN2             | T2 IGBT PWM signal  |  |  |  |

| 17  | GND                | Primary side ground | 18  | PT2-1           | External PT2 pin1   |  |  |  |

| 19  | PT2-2              | External PT2 pin2   | 20  | NC              | Free                |  |  |  |

| 21  | GND                | Primary side ground | 22  | IN3             | T3 PWM signal       |  |  |  |

| 23  | GND                | Primary side ground | 24  | IN4             | T4 PWM signal       |  |  |  |

| 25  | GND                | Primary side ground | 26  | IN5             | T5 PWM signal       |  |  |  |

| 27  | GND                | Primary side ground | 28  | IN6             | T6 PWM signal       |  |  |  |

| 29  | GND                | Primary side ground | 30  | FOUT            | Frequency output    |  |  |  |

# P8 pin definition:

| Pin | Name      | Description        | Pin | Name      | Description        |

|-----|-----------|--------------------|-----|-----------|--------------------|

| 1   | Vcesat-T5 | T5 detected signal | 7   | NC        | The pin is removed |

| 2   | 15V-T5    | T5_15V             | 8   | Vcesat-T1 | T1 detected signal |

| 3   | OFF-T5    | T5 turn-off signal | 9   | 15V-T1    | T1_15V             |

| 4   | ACOM-T5   | T5 GND             | 10  | OFF-T1    | T1 turn-off signal |

| 5   | ON-T5     | T5 turn-on signal  | 11  | ACOM-T1   | T1 GND             |

| 6   | NC        | The pin is removed | 12  | ON-T1     | T1 turn-on signal  |

# P10 pin definition:

| Pin | Name      | Description        | Pin | Name      | Description        |

|-----|-----------|--------------------|-----|-----------|--------------------|

| 1   | Vcesat-T3 | T3 detected signal | 7   | NC        | The pin is removed |

| 2   | 15V-T3    | T3_15V             | 8   | Vcesat-T2 | T2 detected signal |

| 3   | OFF-T3    | T3 turn-off signal | 9   | 15V-T2    | T2_15V             |

| 4   | ACOM-T3   | T3 GND             | 10  | OFF-T2    | T2 turn-off signal |

| 5   | ON-T3     | T3 turn-on signal  | 11  | ACOM-T2   | T2 GND             |

| 6   | NC        | The pin is removed | 12  | ON-T2     | T2 turn-on signal  |

#### P12, P23 pin definition: Pin Description Pin Name Name Description 7 Vcesat-T4 T4 detected signal NC 1 The pin is removed 15V-T4 T4\_15V 8 Vcesat-T6 T6 detected signal 2 9 3 OFF-T4 T4 turn-off signal 15V-T6 $T6_{15V}$ 4 ACOM-T4 T4 GND 10 OFF-T6 T6 turn-off signal T6 GND 5 ON-T4 11 T4 turn-on signal ACOM-T6 12 6 NC ON-T6 The pin is removed T6 turn-on signal

#### P16 pin definition:

| Pin | Name    | Description                 | Pin | Name   | Description                  |

|-----|---------|-----------------------------|-----|--------|------------------------------|

| 1   | -15V-T4 | T4 negative voltage         | 9   | NTC9   | Module 9 temperature signal  |

| 2   | GND-T4  | T4 GND                      | 10  | NC     | The pin is removed           |

| 3   | GND-T4  | T4 GND                      | 11  | NC     | The pin is removed           |

| 4   | NTC1    | Module 1 temperature signal | 12  | NC     | The pin is removed           |

| 5   | NTC3    | Module 3 temperature signal | 13  | NTC10  | Module 10 temperature signal |

| 6   | NTC4    | Module 4 temperature signal | 14  | NTC12  | Module 12 temperature signal |

| 7   | NTC6    | Module 6 temperature signal | 15  | GND-T4 | T4 GND                       |

| 8   | NTC7    | Module 7 temperature signal |     |        |                              |

#### P18 pin definition:

| Pin | Name   | Description                 | Pin | Name  | Description                  |

|-----|--------|-----------------------------|-----|-------|------------------------------|

| 1   | 15V-T4 | T4 15V                      | 4   | NTC5  | Module 5 temperature signal  |

| 2   | GND-T4 | T4 GND                      | 5   | NTC8  | Module 8 temperature signal  |

| 3   | NTC2   | Module 2 temperature signal | 6   | NTC11 | Module 11 temperature signal |

#### P20 pin definition:

| Pin | Name  | Description       | Pin | Name  | Description       |

|-----|-------|-------------------|-----|-------|-------------------|

| 1   | PT1-1 | External PT1 pin1 | 2   | PT1-2 | External PT1 pin2 |

#### P21 pin definition:

| Pin | Name  | Description       | Pin | Name  | Description       |

|-----|-------|-------------------|-----|-------|-------------------|

| 1   | PT2-1 | External PT2 pin1 | 2   | PT2-2 | External PT2 pin2 |

\*The gate driver samples the temperature signals of 12 modules.

\*NTCx is the temperature signal of module x.

# **Driving parameters**

| Absolute Maximum Ratings        |                                                                                                                                                                                                               |                  |         |       |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|-------|--|--|

| Parameter                       | Note                                                                                                                                                                                                          | Min.             | Max.    | Unit  |  |  |

| V <sub>DC</sub>                 | V <sub>DC</sub> to GND                                                                                                                                                                                        |                  | 15.5    | V     |  |  |

| Logic input and output voltages | Primary side, to GND                                                                                                                                                                                          | 0                | 15.5    | V     |  |  |

| SO output                       | Fault condition                                                                                                                                                                                               |                  | 500     | mA    |  |  |

| Gate peak current               |                                                                                                                                                                                                               |                  | 108     | А     |  |  |

| Output power per channel        | T <sub>A</sub> =85°C                                                                                                                                                                                          |                  | 4       | W     |  |  |

| T                               | Primary to secondary side                                                                                                                                                                                     | 5700             | · · · · |       |  |  |

| Test voltage (50Hz/1min)        | $V_{DC}$ to GND15.5Primary side, to GND015.5Fault condition500Fault condition108 $\Gamma_A=85^{\circ}C$ 4Primary to secondary side5700Secondary to secondary side5700 $\pm 100$ $\pm 250$ $-40$ 8540%@118°C2W | V <sub>RMS</sub> |         |       |  |  |

| CMTI                            |                                                                                                                                                                                                               | ±100             | ±250    | kV/us |  |  |

| Operating temperature           |                                                                                                                                                                                                               | -40              | 85      | °C    |  |  |

| Gate resistance derating        | 40%@118°C                                                                                                                                                                                                     |                  | 2W      |       |  |  |

| Storage temperature             |                                                                                                                                                                                                               | -40              | 85      | °C    |  |  |

#### **Recommended Operating Conditions**

| Parameter       | Note | Min. | Тур. | Max. | Unit |

|-----------------|------|------|------|------|------|

| V <sub>DC</sub> |      |      | 15   |      | V    |

| IN <sub>X</sub> |      |      | 15   |      | V    |

#### **Electrical Characteristics**

| Power supply                         | Note                              | Min | Тур  | Max | Unit |  |

|--------------------------------------|-----------------------------------|-----|------|-----|------|--|

| Power supply current                 | Without load, Note 1              |     | 0.47 |     | А    |  |

| Coupling capacitance                 | Primary to secondary side, Note 2 |     | 12   |     | pF   |  |

| Primary side power n                 |                                   |     |      |     |      |  |

| Threshold                            |                                   |     | 13   |     | V    |  |

| Input and output logi                | c                                 |     |      |     |      |  |

| Input impedance                      |                                   |     | 10   |     | kΩ   |  |

| Turn-on threshold                    | 15V PWM input, high turn on       |     | 8.3  |     | V    |  |

| Turn-off threshold                   | 15V PWM input, high turn on       |     | 4.8  |     | V    |  |

| NTC output level                     |                                   |     | 15   |     | V    |  |

| SOx output potential                 | High normal, low fault (pulse)    |     | 15   |     | V    |  |

| Short-circuit protection             |                                   |     |      |     |      |  |

| V <sub>CE</sub> monitoring threshold |                                   |     | 11.1 |     | V    |  |

| Response time                        | T1, T4, Note 3                    |     | 6.7  |     | us   |  |

|                                      | T2, T3, Note 3                    |     | 8.0  |     | us   |  |

|                                      | T5, T6, Note 3                    |     | 8.2  |     | us   |  |

| Blocking time                        |                                   |     | 90   |     | ms   |  |

| Timing characteristics       |                                   |      |     |     |

|------------------------------|-----------------------------------|------|-----|-----|

| Turn-on delay                | T1, T4, Note 4                    | 850  |     | ns  |

|                              | T2, T3, Note 4                    | 850  |     | ns  |

|                              | T5, T6, Note 4                    | 850  |     | ns  |

| Turn-off delay               | T1, T4, Note 5                    | 850  |     | ns  |

|                              | T2, T3, Note 5                    | 850  |     | ns  |

|                              | T5, T6, Note 5                    | 850  |     | ns  |

|                              | T1, T4, Note 6                    | 250  |     | ns  |

| Rise time                    | T2, T3, Note 6                    | 650  |     | ns  |

|                              | T5, T6, Note 6                    | 250  |     | ns  |

| Fall time                    | T1, T4, Note 7                    | 500  |     | ns  |

|                              | T2, T3, Note 7                    | 700  |     | ns  |

|                              | T5, T6, Note 7                    | 500  |     | ns  |

| Output characteristics       |                                   |      |     |     |

| Gate turn-on voltage         |                                   | 15   |     | V   |

| Gate turn-off voltage        |                                   | -15  |     | V   |

|                              | T1, T4, T5, T6                    | 4.7  |     | kΩ  |

| Gate static impedance        | T2, T3                            | 10   |     | kΩ  |

| <b>Electrical isolation</b>  |                                   |      |     |     |

| Creepage distance            | Primary to secondary side, Note 8 | 15   |     | mm  |

| Clearance distance           | Primary to secondary side         | 14.5 |     | mm  |

| NTC temperature acq          | uisition                          |      |     |     |

| NTC temperature              |                                   | 40   | 125 | °C  |

| acquisition range            |                                   | -40  | 125 | C   |

| NTC signal interval time     | Note 9                            | 1    |     | ms  |

| Fault output                 |                                   |      |     |     |

| Fault signal indication time | Note 10                           | 5    |     | ms  |

| Dead time                    |                                   |      |     |     |

| (T1&T3) (T2&T4) Dead         | Note 11                           | 4    |     | 116 |

| time                         | 1000 11                           | +    |     | us  |

| Short pulse suppression      | n                                 |      |     |     |

| Short pulse filtering time   | Note 12                           |      | 400 | ns  |

Unless otherwise specified, all data are based on +25°C and V<sub>IN</sub>=15V.

#### Note:

- 1. Power supply current: connected to IGBT, but no PWM input;

- 2. Coupling capacitance: the values of coupling capacitance are within the range of values given in the table;

- 3. Response time: the time from the occurrence of the fault to the start of soft shut down;

- 4. Turn-on delay: the time required to transmit the rising edge of the PWM signal input from the primary side to the rising edge of the gate driver of the secondary side when the IGBT is not connected;

- 5. Turn-off delay: the time required to transmit the falling edge of the PWM signal input from the primary side to the falling edge of the gate driver of the secondary side when the IGBT is not connected;

- 6. Rise Time: the amount of time from 10% of the gate turn-off voltage(-15V) to 90% of the gate turn-on voltage(+15V);

- 7. Fall Time: the amount of time from 90% of the gate turn-on voltage(+15V) to the gate turn-off voltage(-15V);

- 8. Creepage distance: refer to IEC61800-5-1-2007;

- 9. NTC signal interval time: the period of time that an NTC signal output waits for a high level from one NTC signal output to another NTC signal output;

- 10. Fault signal indication time: fault signal is high when normal, if the gate driver detects a fault, the fault signal first waits for low level for 5ms, then outputs the fault code;

- 11. Dead time: when the time set by the control board has no deadband or is less than 4µs, the driver board itself will have a 4µs deadband; when the time set by the control board is more than 4µs, it will be executed according to the control board time;

- 12. Short pulse filtering time: the maximum short pulse that can be filtered out is 400ns, which may be less than this value in practice.

### **Function description**

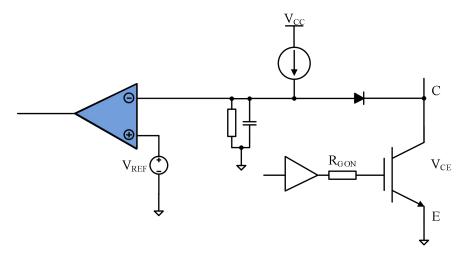

#### Short-circuit protection

The driving circuit determines whether the IGBT is in a short-circuit state by detecting the collector voltage  $V_{CE}$  when the IGBT turns on.

The  $V_{CE}$  voltage is detected by high-voltage diodes. When the  $V_{CE}$  voltage exceeds the set threshold, the gate driver determines that the IGBT is in a short-circuit state and returns the fault to the master computer at the same time. The gate driver will turn off the IGBT according to the order of turning off the IGBT outside first and then the IGBT inside.

Fig. 5 V<sub>CE</sub> desaturation detection circuit

#### ◆ Undervoltage protection

The driver board monitors the positive and negative power supply of the secondary side at the same time. When the absolute value of the positive or negative voltage of the secondary side is lower than the threshold voltage, the driving circuit determines that an undervoltage fault has occurred and will feed back a fault signal to the master computer. The gate driver will turn off the IGBT according to the order of turning off the IGBT outside first and then the IGBT inside.

For IGBT bridge arms, Firstack intelligent gate driver strongly suggests that any IGBT should not work undervoltage. Because of the existence of  $C_{GC}$ , when an IGBT in the bridge arm is turned on, its high dv/dt can be coupled to another IGBT through  $C_{GC}$ , which leads to a slight turn-on of IGBT. At the same time, low gate voltage will increase the switching loss of IGBT.

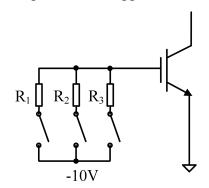

#### Muti-level turn-off (reserved)

In some applications with large stray inductance, such as NPC I-type 3-level large commutation circuit, each time the IGBT is turned off, it will face the risk of excessive turn-off peaks. Due to the limitation of the thermal capacitance of TVS, active clamping technology is not suitable for these occasions, and the muti-level turn-off technology can play a significant role at this time. By using different turn-off resistances during the turn-off process, the entire turn-off process is optimized to suppress the turn-off peak.

Fig. 6 Muti-level turn-off schematic

#### • Short pulse suppression

In many applications, the module may encounter a short pulse situation, and the IGBT will face the risk of too high turn-off peaks every time the IGBT is turned off by a short pulse. We detect the time of the input signal, when the time is less than 400ns, the signal will be filtered out directly, which needs to be verified according to the actual test situation.

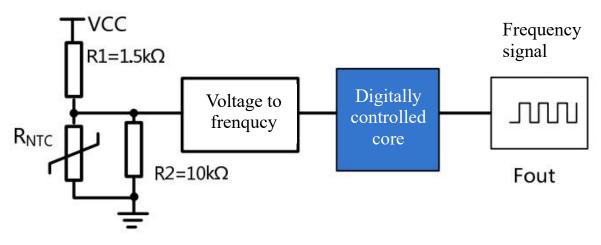

#### ♦ NTC sampling

With the advancement of module packaging technology, more and more modules begin to integrate temperature sensors internally, and NTC is one of these ways. Modules like PrimePACK<sup>TM</sup>, EconoDUAL<sup>TM</sup> and so on have NTC integrated internally.

The Firstack intelligent gate driver integrates a temperature monitoring circuit that converts the temperature signal into a frequency signal via a voltage-to-frequency conversion circuit, and informs the master computer of the frequency signal via an isolation device.

Fig. 7 Temperature monitoring schematic

The driver core outputs the NTC with the highest temperature among the 12-channel IGBTs to the main control via a frequency signal. The output frequency corresponds to the NTC resistance as follows:

Fout =

$$\left(0.1 + \frac{8 * Rntc}{15 + 11.5 * Rntc}\right) * 32.768$$

\*Note: Fout in kHz; Rntc in k $\Omega$ .

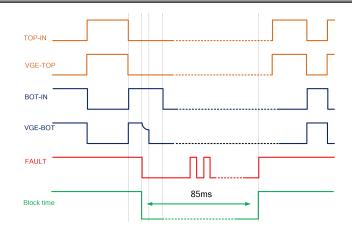

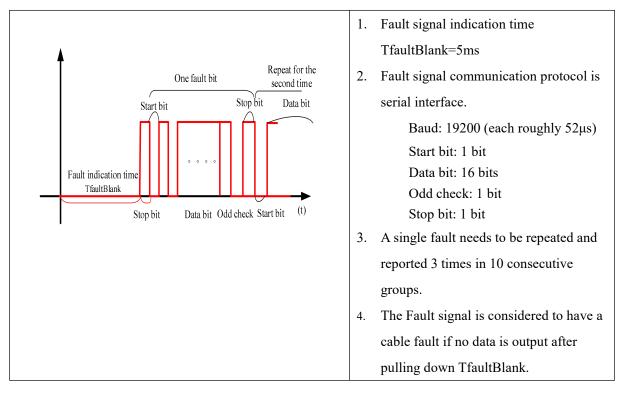

## ◆ Fault code return (reserved)

As large-scale grid integration of new energy sources becomes more and more common, the requirements for converter reliability are becoming higher and higher. The statistics of the types and frequency of failures occurring during field operation and the analysis of the causes after serious failures are also becoming more and more important.

The traditional gate driver design, which only informs the master computer that a fault has occurred when a fault occurs, is becoming less and less able to meet customers' needs. In order to provide more fault information to the customers, on the basis of the original 0/1, we have added a fault communication function, which informs the master computer of the fault category and the timing of the fault occurrence by coding.

#### Fig. 8 Fault communication schematic

The specific fault codes are shown below:

| Symbol       | Conditions                                                                   | Min | Туре | Max | Unit |

|--------------|------------------------------------------------------------------------------|-----|------|-----|------|

| Fault        |                                                                              |     |      | 1   |      |

| TfaultBlank  | FAULT signal fault indication time                                           |     | 5    |     | ms   |

| Fault Bit no | bte: $0 - 15$ If fault is Free, the fault bit holds default high             | '1' |      |     |      |

| 0            | IGBT 1 (top IGBT) short-circuit fault; 1 for normal;<br>0 for fault          |     | Bool |     |      |

| 1            | IGBT 1 (top IGBT) power supply undervoltage; 1 for normal; 0 for fault       |     | Bool |     |      |

| 2            | IGBT 2 (bottom IGBT) short-circuit fault; 1 for normal; 0 for fault          |     | Bool |     |      |

| 3            | IGBT 2 (bottom IGBT) power supply undervoltage;<br>1 for normal; 0 for fault |     | Bool |     |      |

| 4            | IGBT 3 short-circuit fault; 1 for normal; 0 for fault                        |     | Bool |     |      |

| 5            | IGBT 3 power supply undervoltage; 1 for normal; 0 for fault                  |     | Bool |     |      |

| 6            | IGBT 4 short-circuit fault; 1 for normal; 0 for fault                        |     | Bool |     |      |

| 7            | IGBT 4 power supply undervoltage; 1 for normal; 0 for fault                  |     | Bool |     |      |

| 8            | IGBT 5 short-circuit fault; 1 for normal; 0 for fault                        |     | Bool |     |      |

| 9            | IGBT 5 power supply undervoltage; 1 for normal; 0 for fault                  |     | Bool |     |      |

| 10           | IGBT 6 short-circuit fault; 1 for normal; 0 for fault                        |     | Bool |     |      |

| 11           | IGBT 6 power supply undervoltage; 1 for normal; 0 for fault                  |     | Bool |     |      |

#### **ED-WP-CB**

| 12(Reserved) | Top IGBT gate monitoring; 1 for normal; 0 for fault    | Bool |  |

|--------------|--------------------------------------------------------|------|--|

| 13(Reserved) | Bottom IGBT gate monitoring; 1 for normal; 0 for fault | Bool |  |

| 14(Reserved) | Overheating fault; 1 for normal; 0 for fault           | Bool |  |

| 15           | Short pulse; 1 for normal; 0 for fault                 | Bool |  |

Fig. 9 Fault communication timing diagram

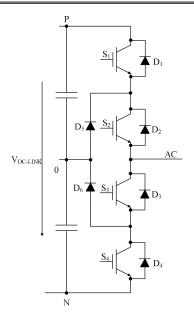

#### ◆ Intelligent fault management system

In NPC I-type 3-level, the DC bus voltage  $V_{DC-LINK}$  is higher than the withstand voltage value of any IGBT, so whether in normal operation or fault condition, it must be ensured that the IGBT outside  $S_4(S_1)$  is turned off before the IGBT outside  $S_3(S_2)$ , otherwise  $S_3(S_2)$  will be damaged because of withstanding the full DC bus voltage  $V_{DC-LINK}$  alone.

Fig. 10 NPC I-type 3-level topology

In the traditional I-type 3-level gate driver design, the correct turn-off timing is generally ensured by the master computer, for example, when a short-circuit fault occurs in  $S_3$ , the driver board first informs the master computer of the fault signal of  $S_3$ , and then the master computer will unify and coordinate the turn-off timing, and thus there are also several risks as follows:

1, Short-circuit protection time exceeds the maximum withstand time of IGBT:  $S_3$  itself short-circuit detection time is generally about 8µs, plus the fault communication time, the master computer filtering time, as well as the turn-off time of  $S_4$  (high-voltage high-power module turn-off time is generally longer, in the range of 4~6µs), the entire protection time will be more than 10µs, which also exceeds the short-circuit safety of the IGBT operating range;

2, Protection is dependent on the master computer: from the single point of failure analysis, when the master computer fails, the protection can not be completed properly, there are security risks.

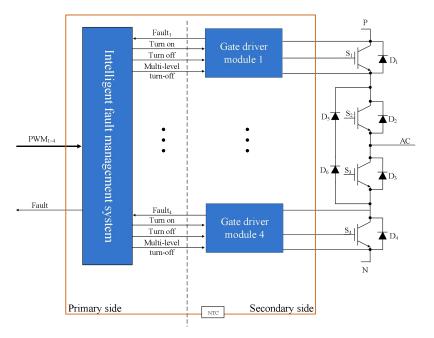

Another risk is that traditional driver IC and even the vast majority of plug-and-play drivers tend to directly turn off the IGBT in the event of an undervoltage fault, which is not applicable to the NPC I-type 3-level scheme, resulting in a significant safety risk. Based on the analysis above, Firstack has developed a drive solution specifically for NPC I-type 3-levels: by integrating Firstack's unique "intelligent fault management system" on the primary side, it ensures the correct turn-off timing under any operating conditions.

Fig. 11 Intelligent fault management system

The intelligent fault management system will monitor all four PWM signals and all four IGBT status in real time, and then give the optimal operation instruction through Firstack's unique control algorithm. When the whole machine is in continuous operation and the following faults occur, safety can be ensured:

1: PWM command fault: when the master computer is disturbed and sends wrong commands, or the PWM transmission path is disturbed and wrong commands appear on the gate driver side;

2: Connector disconnection: in the operation of the whole machine, the connector is disconnected due to vibration and other factors, resulting in uncontrolled PWM command status;

3: Gate driver power supply abnormality: in the operation of the whole machine, because of the failure of the power supply terminal, causing the gate driver power supply abnormality.4: Short-circuit/undervoltage fault.

# **Ordering information**

ED-WP-CB supports different models of modules from multiple manufacturers. If you have a purchase request, please contact us, and we can provide the gate driver that best meets your needs.

# **Technical support**

Firstack's professional team will provide you with business consultation and technical support. Please contact the Firstack technical sales team if you require the application manual for further information of the technical application.

# Legal disclaimer

This manual gives a detailed introduction about the product, but cannot promise to provide specific parameters. No warranty or guarantee, express or implied, is given herein as to the delivery, performance or applicability of the product.

Firstack reserves the right to modify technical data and product specifications at any time without prior notice. Firstack's general payment terms and conditions apply.

# **Contact information**

Tel: +86-571 8817 2737

Fax: +86-571 8817 3973

Website: www.firstack.com

Email: <u>fsales@firstack.com</u>

Address: 4-5/F, Building/5, Xizi Wisdom Park, No.1279 Tongxie Road, Hangzhou, China